Nachdem ich die auf der Webseite von AnalogDevices gefundenen MOSFET-Symbole vorgestellt

und auch mit einer simplen Inverter-Schaltung das Funktionieren der benutzten MOSFET-Modelle

demonstriert hatte, fand ich es schade, es einfach dabei zu belassen.

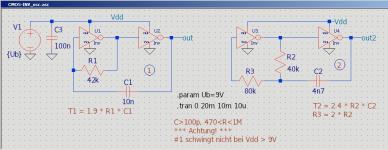

Also habe ich ein Symbol für den Inverter entworfen (das LTspice Inverter-Symbol kann man nicht

benutzen!), die Inverter-Schaltung als Mikro-Modell in einen Subcircuit verpackt und ein wenig damit

experimentiert. Hier und heute stelle ich in diesem ersten Teil zunächst zwei Oszillatorschaltungen

vor, so wie man sie allenthalben sieht und kennt. Nichts Besonderes, und deshalb gibt es auch nicht viel

dazu zu sagen.

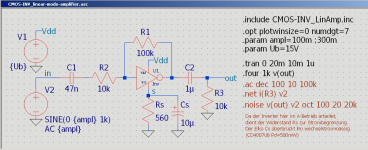

Die zweite Schaltung ist die analoge Verwendung als linearer Verstärker. Dieser ist in diesem

Beispiel nur mit einer positiven Spannung betrieben, aber da der Inverter zwei Spannungsanschlüsse

Vdd und Vss besitzt, ist prinzipiell auch ein Betrieb mit z.B. + - 5 Volt oder auch ungleichen +9 Volt,

-5 Volt möglich. Bei gepolten Kondensatoren wie Elkos ist da auf die richtige Polung zu achten oder

man verwendet einen bipolaren Typ!

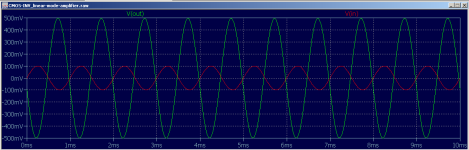

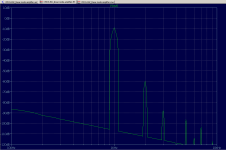

Mit einer Eingangsspannung von 100mV und 5-facher Verstärkung bleiben die Verzerrungen unter

0.3%. Die Verstärkung kann man mit den Widerständen nicht beliebig einstellen wie bei einem

Opamp, übertreibt man es, folgt die “Strafe” als erhöhter Klirrfaktor auf dem Fusse.

Braucht man mehr Verstärkung, muss man eben mehrere Stufen hintereinander schalten.

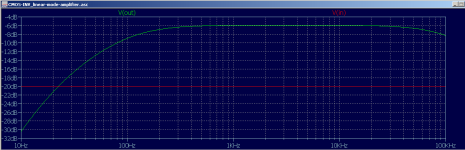

Der Frequenzbereich ist, wie aus dem AC-Plot ersichtlich, nicht so super, schafft aber immerhin den

Audiobereich. Den Abfall der tiefen Frequenzen kann man durch einen grösseren Eingangskondensator

beheben.

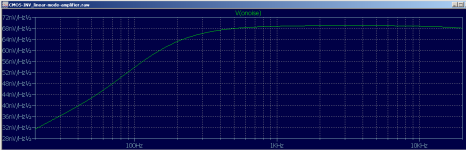

Rauschen beträgt über den Audio-Frequenzbereich ca. 10uV, nicht besonders gut, aber auch nicht

besonders schlecht, mehr durfte man – meine ich – nicht erwarten.

Da der Inverter als linearer Verstärker in Klasse A betrieben wird, muss man auf die Verlustleistung

achten und (wahrscheinlich) den Stromfluss begrenzen! Messergebnisse bei der TRAN-Simulation in der SPICE error

log.

Alle Dateien befinden sich wie immer im ZIP-Archiv.

RudiS

und auch mit einer simplen Inverter-Schaltung das Funktionieren der benutzten MOSFET-Modelle

demonstriert hatte, fand ich es schade, es einfach dabei zu belassen.

Also habe ich ein Symbol für den Inverter entworfen (das LTspice Inverter-Symbol kann man nicht

benutzen!), die Inverter-Schaltung als Mikro-Modell in einen Subcircuit verpackt und ein wenig damit

experimentiert. Hier und heute stelle ich in diesem ersten Teil zunächst zwei Oszillatorschaltungen

vor, so wie man sie allenthalben sieht und kennt. Nichts Besonderes, und deshalb gibt es auch nicht viel

dazu zu sagen.

Die zweite Schaltung ist die analoge Verwendung als linearer Verstärker. Dieser ist in diesem

Beispiel nur mit einer positiven Spannung betrieben, aber da der Inverter zwei Spannungsanschlüsse

Vdd und Vss besitzt, ist prinzipiell auch ein Betrieb mit z.B. + - 5 Volt oder auch ungleichen +9 Volt,

-5 Volt möglich. Bei gepolten Kondensatoren wie Elkos ist da auf die richtige Polung zu achten oder

man verwendet einen bipolaren Typ!

Mit einer Eingangsspannung von 100mV und 5-facher Verstärkung bleiben die Verzerrungen unter

0.3%. Die Verstärkung kann man mit den Widerständen nicht beliebig einstellen wie bei einem

Opamp, übertreibt man es, folgt die “Strafe” als erhöhter Klirrfaktor auf dem Fusse.

Braucht man mehr Verstärkung, muss man eben mehrere Stufen hintereinander schalten.

Der Frequenzbereich ist, wie aus dem AC-Plot ersichtlich, nicht so super, schafft aber immerhin den

Audiobereich. Den Abfall der tiefen Frequenzen kann man durch einen grösseren Eingangskondensator

beheben.

Rauschen beträgt über den Audio-Frequenzbereich ca. 10uV, nicht besonders gut, aber auch nicht

besonders schlecht, mehr durfte man – meine ich – nicht erwarten.

Da der Inverter als linearer Verstärker in Klasse A betrieben wird, muss man auf die Verlustleistung

achten und (wahrscheinlich) den Stromfluss begrenzen! Messergebnisse bei der TRAN-Simulation in der SPICE error

log.

Alle Dateien befinden sich wie immer im ZIP-Archiv.

RudiS

Anhänge

-

01__CMOS-INV_Osc_Schema.png27,7 KB · Aufrufe: 4

01__CMOS-INV_Osc_Schema.png27,7 KB · Aufrufe: 4 -

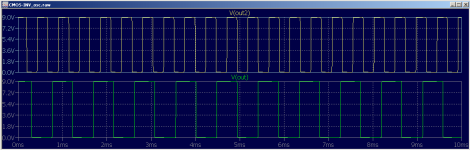

02__CMOS-INV_Osc_Plot.png9,8 KB · Aufrufe: 4

02__CMOS-INV_Osc_Plot.png9,8 KB · Aufrufe: 4 -

03__CMOS-INV_LinAmp_Schema.png38,5 KB · Aufrufe: 3

03__CMOS-INV_LinAmp_Schema.png38,5 KB · Aufrufe: 3 -

04__CMOS-INV_LinAmp_TRAN-Plot.png13,5 KB · Aufrufe: 3

04__CMOS-INV_LinAmp_TRAN-Plot.png13,5 KB · Aufrufe: 3 -

05__CMOS-INV_LinAmp_TRAN-FFT.png15,1 KB · Aufrufe: 2

05__CMOS-INV_LinAmp_TRAN-FFT.png15,1 KB · Aufrufe: 2 -

06__CMOS-INV_LinAmp_AC-Plot.png11,1 KB · Aufrufe: 2

06__CMOS-INV_LinAmp_AC-Plot.png11,1 KB · Aufrufe: 2 -

07__CMOS-INV_LinAmp_NOISE-Plot.png11,4 KB · Aufrufe: 4

07__CMOS-INV_LinAmp_NOISE-Plot.png11,4 KB · Aufrufe: 4 -

CMOS-INV_Teil 1.zip154,4 KB · Aufrufe: 0