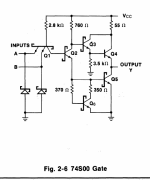

Die vorliegende Schaltung entstand mehr oder weniger durch Zufall: beim Blättern durch ein Fairchild-Datenbuch

sah ich diese NAND-Schaltung mit sogenannten Schottky-Transistoren. Deren Zweck ist es zu verhindern, dass der Transistor in Sättigung gerät,

da es andernfalls zu einer Zeitverzögerung (propagation delay) kommt, weil die Ladung an der Basis erst abgebaut werden muss,

ehe der Transistor vom ON in den OFF-Zustand wechseln kann.

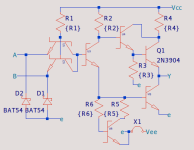

Obwohl im allgemeinen digitale Schaltungen gar nicht so mein Ding ist, reizte es mich, diese Schaltung, insbesondere den Schottky-Transistor,

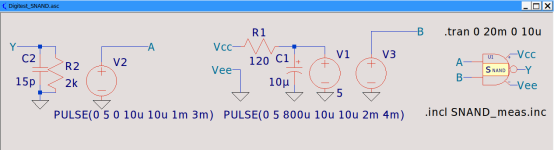

mit diskreten Bauteilen nachzuahmen. Dazu habe ich zuerst den Schottky-Transistor in einen Subcircuit verpackt und später dann das

ganze NAND.

Das Dumme ist nur, da ich überhaupt keine Erfahrung mit digitalen Dingen habe, kann ich selber das Ergebnis gar nicht beurteilen.

Vielleicht ist aber jemand unter den Lesern, der sich in der Materie auskennt und etwas dazu sagen kann. Es würde mich freuen.

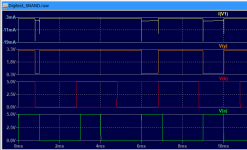

Immerhin, LOW und HIGH Pegel scheinen im TTL-angemessenen Bereich zu liegen. Im Plot sieht man auch sehr schön, dass auf der Speisespannungsleitung

unschöne Spikes in den Schaltphasen entstehen -- keine Ahnung, ob das bei echten 74LS-ICs auch so ist -- und die auch mit Elko-Pufferung

nicht gänzlich verschwinden.

Einige Messergebnisse finden sich in der LTspice error log.

RudiS

sah ich diese NAND-Schaltung mit sogenannten Schottky-Transistoren. Deren Zweck ist es zu verhindern, dass der Transistor in Sättigung gerät,

da es andernfalls zu einer Zeitverzögerung (propagation delay) kommt, weil die Ladung an der Basis erst abgebaut werden muss,

ehe der Transistor vom ON in den OFF-Zustand wechseln kann.

Obwohl im allgemeinen digitale Schaltungen gar nicht so mein Ding ist, reizte es mich, diese Schaltung, insbesondere den Schottky-Transistor,

mit diskreten Bauteilen nachzuahmen. Dazu habe ich zuerst den Schottky-Transistor in einen Subcircuit verpackt und später dann das

ganze NAND.

Das Dumme ist nur, da ich überhaupt keine Erfahrung mit digitalen Dingen habe, kann ich selber das Ergebnis gar nicht beurteilen.

Vielleicht ist aber jemand unter den Lesern, der sich in der Materie auskennt und etwas dazu sagen kann. Es würde mich freuen.

Immerhin, LOW und HIGH Pegel scheinen im TTL-angemessenen Bereich zu liegen. Im Plot sieht man auch sehr schön, dass auf der Speisespannungsleitung

unschöne Spikes in den Schaltphasen entstehen -- keine Ahnung, ob das bei echten 74LS-ICs auch so ist -- und die auch mit Elko-Pufferung

nicht gänzlich verschwinden.

Einige Messergebnisse finden sich in der LTspice error log.

RudiS

Anhänge

Zuletzt bearbeitet: