JFET Stromquelle: Herleitung und Vorselektion

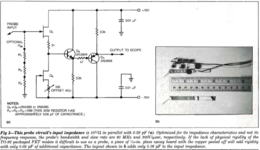

Für die Messung der Bandbreite von LC Schwingkreisen wollte ich mir einen HF-Tastkopf mit sehr kleiner Eingangskapazität bauen. Nach vielen Irrungen und Wirrungen bin ich schlussendlich bei einem Schaltungsvorschlag von Bob Pease gelandet, der tatsächlich meine Anforderungen erfüllt. Ich werde noch einen separaten Post dazu erstellen.Dieser HF-Tastkopf verwendet einen JFET als Sourcefolger am Eingang. In der Source liegt auch noch gleich eine Stromquelle mit JFET, die den Arbeitspunkt festlegt.

Wer kennt Bob Pease? Bob war ein genialer Analog Entwickler bei National Semiconductors. Er wird auf Seite 3 der Artikelserie unten vorgestellt. Er hat Generationen von Ingenieuren mit seinen praktischen Ansätzen beeinflusst und ist auch heute noch eine Quelle für Know-How.

Code:

Bitte,

Anmelden

oder

Registrieren to view codes content!

RudiS hat in mehreren, ausgezeichneten Artikeln das JFET Modell und die einzelnen Parameter detailliert vorgestellt. Danke RudiS!

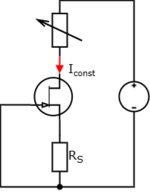

Einfache JFET Konstantstromquelle

idss und vp extrahieren

vto und beta

lambda

Ich simulierte die Schaltung zuerst in LTspice und sie hatte hervorragende Werte bezüglich Frequenzgang und Eingangskapazität. Beim Nachbau der Schaltung merkte ich aber schnell, dass die Auslegung der Stromquelle mit Q2 stark von der Simulation abwich. Der Grund sind die starken Streuungen der JFET Parameter von realen JFET.

In der Schaltung ist ein Trimmer vorgesehen, um den Arbeitspunkt einzustellen. Das ist aber bei HF-Schaltungen nicht unbedingt erwünscht, da ein Trimmer doch recht gross ist.

Will man den Trimmer vermeiden, kann man den Transistor relativ einfach vorselektieren und den Source Widerstand berechnen.

Ich habe auf meiner Webseite im Blog JFET Stromquelle: Herleitung und Vorselektion das Verfahren genau beschrieben und auch gleich ein kleines Java Script eingefügt, mit dem man den Source Widerstand aufgrund der gemessenen Werte berechnen kann.

Ich werde hier zusammengefasst die Ergebnisse vorstellen und den praktischen Ansatz erklären.

Stromquelle mit einem N-Kanal JFET

1. Die Shockley-Gleichung

[math][/math]Die Grundlage für die Berechnung einer Stromquelle mit einem JFET ist die Shockley-Gleichung für den Sättigungsbereich:[math]I_D = I_{DSS} \cdot \left(1 - \frac{V_{GS}}{V_{GS(off)}}\right)^2[/math]Um den benötigten Source-Widerstand [imath]R_S[/imath] zu finden, stellen wir die Gleichung nach [imath] V_{GS} [/imath] um:

[math] V_{GS} = V_{GS(off)} \cdot \left(1 - \sqrt{\frac{I_D}{I_{DSS}}}\right) [/math]Der Widerstand berechnet sich dann aus dem Ohmschen Gesetz am Source-Pin:

[math]R_S = \frac{|V_{GS}|}{I_D}[/math]

2. Physikalische Herleitung

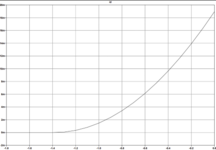

RudiS hat die Grundlagen schon beschrieben. Hier aber noch ein etwas anderer Blickwinkel:Die Shockley-Gleichung beschreibt den JFET im Sättigungsbereich. Die quadratische Charakteristik resultiert aus der Geometrie der Raumladungszone (RLZ):

- Steuerung: Eine negative Spannung [imath]V_{GS}[/imath] vergrößert die RLZ am Gate-Kanal-Übergang.

- Kanalquerschnitt: Die effektive Breite [imath]w[/imath] des leitenden Kanals nimmt ab. Da die Ausdehnung der RLZ proportional zur Wurzel der Spannung ist ([imath](x \propto \sqrt{V}[/imath]), ändert sich der Leitwert des Kanals.

- Integration: Betrachtet man den Ladungstransport über die gesamte Kanallänge [imath]L[/imath] und berücksichtigt, dass bei Erreichen von der Kanal "abgeschnürt" (Pinch-off) wird, ergibt sich durch Integration der Ladungsdichte die parabolische Form:

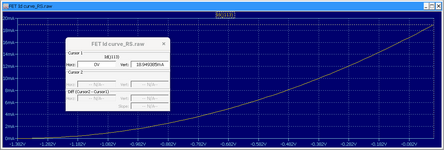

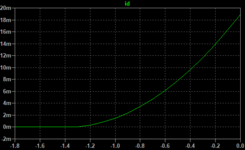

Kennlinie des LTspice Models J113 N-Kanal JFET

2. Parameter aus dem LTspice Modell

Die Parameter des Models des J113 sind:

Code:

Bitte,

Anmelden

oder

Registrieren to view codes content!

- [imath]V_{GS(off)} = Vto = -1,382 \, \text{V}[/imath]

- [imath]I_{DSS} = \text{Beta} \cdot Vto^2 = 9,109\text{m} \cdot (-1,382)^2 \approx 17,4 \, \text{mA}[/imath]

Vto (Threshold Voltage): Entspricht direkt der Abschnürspannung [imath](V_{GS(off)} )[/imath]

Die Erklärung dazu findet sich im Post von RudiS vto und beta.

Der Zusammenhang zur Shockley-Gleichung:

LTspice verwendet intern eine leicht andere Form der Gleichung, die sich aber direkt in die Shockley-Form überführen lässt:

[math]I_D = \text{Beta} \cdot (V_{GS} - \text{Vto})^2[/math]Vergleicht man dies mit der klassischen Form [imath] I_D = I_{DSS} \cdot (1 - \frac{V_{GS}}{V_{GS(off)}})^2 [/imath], ergibt sich für den Kurzschlussstrom [imath] I_{DSS} [/imath] (bei [imath]V_{GS} = 0 [/imath] )

[math]I_{DSS} = \text{Beta} \cdot \text{Vto}^2[/math]Für den J113 bedeutet dies:

- [imath]\text{Beta} = 9,109\text{ mA/V}^2 (9.109m[/imath])

- [imath]\text{Vto} = -1,382\text{ V}[/imath]

- [imath]I_{DSS} = 0,009109 \cdot (-1,382)^2 \approx \mathbf{17,4\text{ mA}}[/imath]

2. Vorselektion (Testaufbau)

Da der J113 extreme Streuwerte besitzt ([imath]I_{DSS}[/imath] von 2mA bis 20mA+), müssen Transistoren für eine 8mA Quelle vorselektiert werden:Messung von [imath]I_{DSS}[/imath]:

- Drain an +15V DC anschließen.

- Gate und Source direkt an Masse legen.

- Strom [imath]I_{D}[/imath] messen: Dies ist dein individuelles [imath]I_{DSS}[/imath] .

- Kriterium: Nur Transistoren mit [imath]I_{DSS} > 8\text{ mA}[/imath] verwenden!

- Drain an +15V, Gate an Masse.

- Source über ein Voltmeter (hochohmig, 10MΩ) gegen Masse messen.

- Die angezeigte Spannung entspricht nahezu [imath]|V_{GS(off)}|[/imath].

3. [imath]R_S[/imath] berechnen

Entweder mit meinem Java-Script hier: Blogpostoder gemäss der Formel im Abschnitt 1.

4. Simulieren

Im Anhang noch meine Simulations-Testschaltung "JFET_Test_model. Die Kennlinie erhält man mit ctrl L und dann rechtsclick auf das Log und dann "Plot .step'ed .meas data"

5. Weitere Gedanken

Wie schon RudiS erwähnt hat, ist diese Stromquelle recht Temperatursensitiv.Anhänge

Zuletzt bearbeitet von einem Moderator: