Tjo, in dieser Richtung fällt mir nicht mehr viel ein.

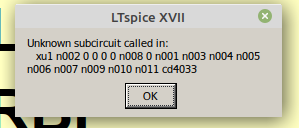

Gibt es einen LTspice-Crack, der sich diese CD4033-Simulation angucken würde?

@Udo, bist Du noch mit Hern Marcos Alonso im Kontakt? Vielleicht würde er sich das ja ansehen.

Mein Plan C:

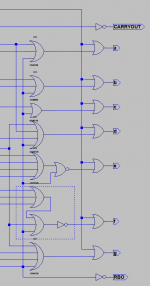

Man erstellt das Modell genauso wie die anderen Modelle in der CD4000.lib:

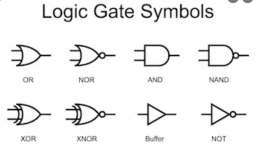

Aus der Beziehung zwischen Eingangs- und Ausgangssignalen konstruiert man Logik- und Zähler-Funktionen und gibt noch Verzögerungszeiten an. Dazu benutzt man die Logik-Ausdrücke aus der CD4000.lib, die LTspice-Spice ja versteht.

Dazu muß man natürlich wissen, was in den Zeilen gemacht wird. Wo gibt es wohl eine Dokumentation darüber?

Falls es keine gibt, wird es etwas mühsam. Obwohl - für die reinen Logik-Funktionen stelle ich es mir nicht so schwierig vor. Bei getakteten Abläufen dagegen ... naja, fangen wir erstmal mit den Logiken an

.

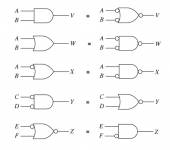

Hier ist z.B. der CD4011, ein 2-fach NAND-Gatter:

Man ahnt zumindest, was in den Zeilen gemacht wird.

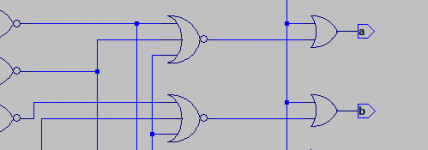

Dies ist natürlich ein einfaches Beispiel. Für den CD4033 kämen außer den Ein- und Ausgangsspannungen auch noch interne Signale hinzu, z.B. der Q-Ausgang von Flip-Flop1#1 und der \Q-Ausgang von Flip-Flop#3, die miteinander exclusiv oderiert werden, um Segment B zu bilden. Oder so. Ich seh' gerade - Ai, Bi und Yi sind offenbar interne Signale bzw. Spannungen.

Mit diesem Ansatz wäre die Simulation vermutlich auch schneller als sie jetzt ist.

Gruß, Frank