Ich hab's geschafft!!!

CMOS Dekadenzähler/-teiler mit dekodierten Ausgängen für 7-Segment-Anzeigen. Ggf. in der SpiceLine VDD=Spannung anpassen. Eingänge: Low < ½ Vdd High >= ½ Vdd Dieses Modell ist exklusiv für ltspiceusers.ch erstellt worden. Man beachte auch das Tool hier: Visualisierung von 7-Segment Anzeige...

www.ltspiceusers.ch

Funktioniert FAST!

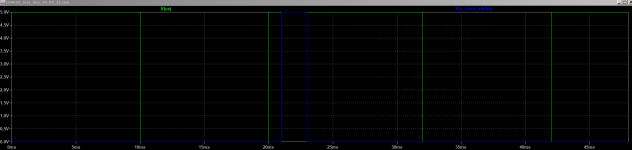

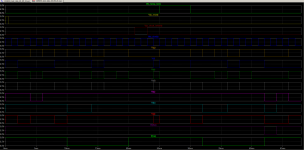

Zum Testen habe ich das originale Timing aus dem Datenblatt nachgebildet, ausgehend von einem Clock-Flanken-Abstand von 1 ms.

Insgesamt brauchen dann nur 48 ms simuliert zu werden, und man kann die Ausgangssignale direkt mit den Vorgaben vergleichen.

Hier sind PULSE(...)-Angaben in Klartext; ich hoffe, sie sind so universeller in Eure jeweilige Schaltungen einzufügen als ein Schaltungsfragment mir Copy&Paste.

s_CLOCK: PULSE(0 5 0 100n 100n 1m 2m)

s_RESET: PULSE(0 5 0 100n 100n 1m)

s_CLOCK_INHIBIT: PULSE(0 5 21m 100n 100n 2m)

s_LAMP_TEST: PULSE(0 5 25m 100n 100n 5m)

s_RBI: PULSE(0 5 0 100n 100n 35m)

spicer, Deine Schaltung funktioniert demnach bis zum Zeitpunkt 22 ms 100%ig!

Der Clock_Inhibit sollte bei 22 ms den Clock einmal unterdrücken, so daß der ganze weitere Ablauf um 2 ms verzögert wird. Bei dieser Simulation hat der Clock_Inhibit aber keine Wirkung,

@Udo , bei mir lief die Simulation ohne Probleme. Ich starte allerdings jede neue Simulation von Euch in einem neuen Ordner. Achso, und ich benutze LTspice IV.

Gruß, Frank