Danke! Ich hatte nur nach "Generate

Extended Listing" gesucht. Der Autor schreibt allerdings "Generate

Expanded Listing". Das fand ich auch bei der Suche, allerdings nur als Einstellung im Control Panel, deshalb suchte ich nicht weiter danach.

In der LTspice-Group findet man über Expanded Listing auch was:

Re: Netlist generation

Ich nehme an, diese Expanded-Listing-Zeilen haben einen LTspice-Spezialsyntax. Aber wir wollen ja auch nicht die ganze Welt beglücken.

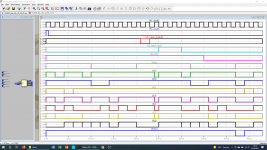

Die logische Seite steht ja jetzt. Die CD4033-Simulation ist IMO erst vollwertig, wenn das Bauteil auch das elektrische und zeitliche Verhalten aus dem Datenblatt hat. Die Simulation ist ja eine Vorstufe des Lötens, und wenn beim Aufbau unerwartete Eigenschaften - wie schwache Belastbarkeit der Ausgänge, niedrige Grenzfrequenz, Schwingungsneigung bei hochohmigen Eingängen, ... - auftreten, kippt beim Bastler die Stimmung. UND DAS WILL KEINER!

Das CD4033-Modell (in seiner Eigenschaft als Muster für künftige CMOS-Modelle) wäre noch flexibler, wenn die Angaben tripdt, td, vhigh usw. nicht in jeder Zeile direkt zugewiesen würden, sondern wenn wie bei den anderen Modellen Variablen benutzt würden, die in der SUBCKT-Zeile definiert sind, z.B. vdd2={vdd1} speed2={speed1}. Vorausgesetzt, dieser Syntax läßt es zu.

Gruß, Frank